ILL Number: 78608032

Yes No Cond

Borrower: AZU

Request Date: 20110608

Lending String: HUH, HUH, RVE, \*MYG

Journal Title: Proceedings /

Volume: Issue:

Month/Year: June 1993

Pages: 538-540

Author:

Title: Hsu, P. and Rozenblit, J.W. and Prince, J.; An Object-Oriented Approach to Hierarchical

Design of Multichip Systems

Imprint: Tampa, FL; VLSI Multilevel Interconnect

Shipping Method: Odyssey

Call #: e TK7874.1582 p

Location:

MaxCost: \$50IFM

Patron: Suantak, Liana Son

Library Address:

University Arizona Libraries

1510 E University

Tucson AZ 85721-0055

Request Type: Article

OCLC# 31792184

Notes: Borrowing Notes; For Book Chapter requests, scan the chapter only, do not lend book. If over your page limit, please CONDITIONAL request. Thank you.

## COMPLETED

JUN 09 2011

DOCUMENT SERVICES

**O**dyssey: 150.135.238.6

**lei: 150.135.238.50**

Address: askddt@u.library.arizona.edu

\*\*\*US Copyright Notice\*\*\*

taw of the United States (Title 17, United States Code) governs the making of reproductions of copyrighted material. in conditions specified in the law, libraries are authorized to furnish a reproduction. One of these specified conditions is that the is not to be "used for any purpose other than private study, scholarship, or research." If a user makes a request for, or later uses, a for purposes in excess of "fair use," that user may be liable for copyright infringement. n reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of

# AN OBJECT-ORIENTED APPROACH FOR THE HIERARCHICAL DESIGN OF VLSI MULTICHIP SYSTEMS<sup>1</sup>

Pochang Hsu, J. W. Rozenblit and J. L. Prince Center for Electronic Packaging Research Department of Electrical and Computer Engineering University of Arizona, Tucson, AZ 85721, U.S.A Tel:(602) 621-8946, Fax: (602) 621-8076

#### **Executive Summary**

Object-oriented approach is applied to develop building blocks (models) of a VLSI multichip system for packaging simulations. In conjunction with hierarchical design, our approach reduces the complexity of modeling and increases reusability of models.

#### Extended Abstract

Interconnections and packages are among the dominant factors that limit the performance of future integrated circuits. This is especially true for high-speed and high-density electronic systems. Advanced VLSI multichip systems usually contain multilevel interconnections and packages which complicate the analysis and design of the entire system. Although advanced CAD tools have been developed for detailed simulations of such systems in different aspects (electrical or thermal/mechanical, etc.) [1], designers rarely pay much attention to important issues such as design data management and automatic simulation model generation which could increase their productivity. Part of the reason is due to the complexity of design database included in multilevel interconnections and the package of a multichip assembly or module such as decomposition (e.g., chips on a board), taxonomy (e.g., lossy or lossless line, MCM substrate or multilayered printed wire board, etc.), coupling (e.g., drivers, receivers and interconnections in a transmission line system, etc.), and design attributes specifications (e.g., power disspation of each chip or substrate dielectric, etc.).

Fortunately, the hierarchical nature of multilevel interconnections and packages in a VLSI system reduces the complexity of representation scheme in the design process. The use of hierarchy involves dividing a system into subsystems and then repeating this operation on subsystems until the complexity of the subsystems is at a desired abstraction level [2]. This increases the efficiency of computer-aided design processing.

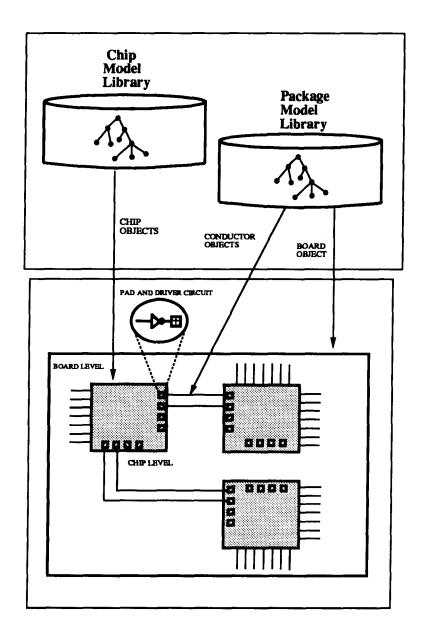

In this paper, an object-oriented approach is applied to represent and develop a design database which encompasses different component models (model base) for multilevel interconnects and packaging structure. The model components are organized in two major libraries termed Chip model library and Package model library. Chip model library includes physical, thermal, and electrical (especially peripheral models such as drivers, receivers, etc.) information of chips with different levels of complexity and abstraction. Package

<sup>&</sup>lt;sup>1</sup>This research is supported in part by Semiconductor Research Corporation.

model library includes models for different types of boards, modules (or only substrates when multichip modules are considered), and multilevel interconnects (which also include discontinuities such as bends, vias, and crossovers, etc.). Automatic model generation for simulation is done by effective interface and coupling between these two major libraries as shown in Figure 1.

Object-oriented design and object-oriented programming support data abstraction (class and objects), inheritance and modularity [3]. The "generalization-specialization", and "whole-part (or component-subcomponent)" concepts [4] provided in object-oriented design are used to facilitate the implementation of taxonomy, decomposition and coupling for the development of design database (libraries) and automatic model generation for simulation. For example, compared with the pMOS/nMOS model in a lossless transmission line simulator UANTL [5], SPICE model is more specialized (with added details). Accordingly, in our implementation of Chip model library, the SPICE pMOS/nMOS model is just an inherited class from the more general UANTL class with specialized parameters being included. As an illustration for decomposition, consider the implementation of a multistage CMOS inverter in Chip model library. Model designers only have to define a cascaded CMOS inverter class with predefined inverter class as its member object (subcomponent). In this manner, not only the complexity of the development of libraries can be reduced, but the reusability of the software building blocks (models) increased. The building of a transmission line system for circuit simulation is accomplished by retrieving models from Packaging model library and Chip model library and then sending messages to those models (objects) to construct a SPICE like network. This is a typical coupling scheme of model generation for simulations.

Currently the described hierarchical structures of Packaging model library and Chip model library for supporting the VLSI multichip system design are implemented in C++ programming language and reside in an existing CAD framework called Packaging Design Support Environment (PDSE) [6] which integrates several software tools for electronic packaging simulation.

### References

- [1] J. L. Prince, O. A. Palusinski and A. C. Cangellaris, "Modeling Packaging Characteristics for High Speed Devices", *Journal of Semicustom ICs*, Vol. 8, No. 4, pp. 30-38, 1991.

- [2] J. W. Rozenblit and Jhyfang Hu, "Integrated knowledge representation and management in simulation-based design generation", *Mathematics and Computers in Simulation*, 34(1992) pp. 261-282.

- [3] Bjarne Stroustrup, The C++ Programming Language, Chapter 12, Addison-Wesley Publishing Company, New York, 1991.

- [4] Ivar Jacobson, Object-oriented Software Engineering, Addison-Wesley Publishing Company, New York, 1992.

- [5] O. A. Palusinski, J. C. Liao, John L. Prince, and Andreas C. Cangellaris, "Simulation of Transients in VLSI Packaging Interconnections," *IEEE Transactions on Components*, *Hybrids, and Manufacturing Technology*, Vol. 13, No. 1, March 1990.pp 160-166.

[6] P. Hsu, S. Voranantakul, J. W. Rozenblit and J. L. Prince, "Intelligent Design Automation of VLSI Interconnects", *Proc. of IEEE 1992 International Phoenix Conference on Computers and Communications*, pp.349-355, Scottsdale, Arizona, 1992.

Figure 1: Simulation model generation for the hierarchical design of a VLSI multichip system.